# Recent Development and Progress in Nonvolatile Memory for Embedded Market

Saied Tehrani, Ph.D. Chief Technology Officer, Spansion Inc.

July 11, 2012

### Outline

# <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header>

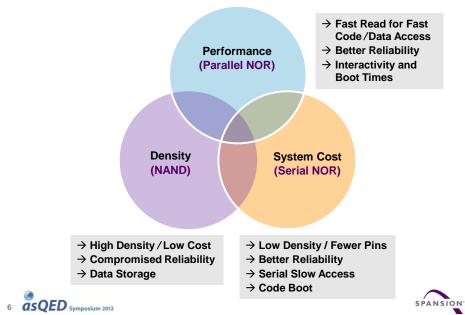

### NOR and NAND Flash for Embedded Market

### **Auto Infotainment**

- Multi-language interfaces, rich graphics, user configuration data

- Parallel NOR for fast boot

- Embedded SLC NAND data storage

### Set-top Box / TV

- Internet and app support drives larger software requirements

- Serial NOR for fast boot

- Embedded SLC NAND for reliable application storage

### Communications

- Multi-mode base stations drive increased software complexity

- Parallel NOR for fast boot

- Embedded SLC NAND data storage

| NAND Flash - Status and Market Needs - NAND Scaling Challenges - Lithography Gaps |       |

|-----------------------------------------------------------------------------------|-------|

| Other Nonvolatile Technolo<br>- Phase Change Memory<br>- Resistive RAM<br>- MRAM  | ogies |

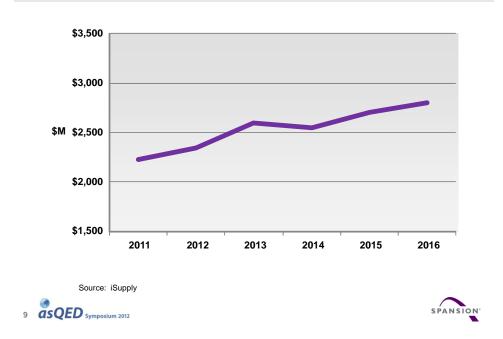

### **Embedded NOR Flash TAM**

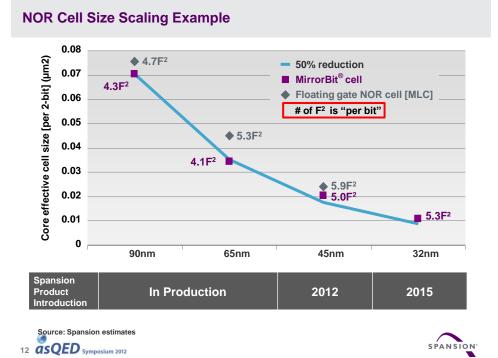

NOR Flash Memory Cell – MirrorBit® Technology **MirrorBit**® WI Gate \\/I wı Top Oxide Tunnel Oxide Proprietary 0 < wı wı Storage Medium WL N p-substrate ÷ WL WL Contact MirrorBit cell stores charge in two physically different locations Non-conducting storage dielectric - Doubles device density Symmetric transistor - Selectable source-drain - Simple, planar structure SPANSION 10 asQED Symposium 2012

| Spansion 45nr               | n Technology                                                                                                    |                                  |                                                                           |    |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------|----|

| CoSi<br>Poly-1<br>ONO       | 55nm<br>Poly-2<br>HDP<br>e = 0.037 μm <sup>2</sup>                                                              | - 46.0%                          | 45nm<br>CoSi<br>Poly 2<br>HDP<br>ONO<br>Cell size = 0.020 μm <sup>2</sup> |    |

| 45nm<br>Technology          | <ul> <li>Junction engine</li> <li>Bit line trench to</li> <li>Optimized prog</li> <li>Performance ar</li> </ul> | o minimize neig<br>ram and erase | hboring bit program disturb<br>algorithms                                 |    |

| 11 <b>asQED</b> Symposium 2 | 012                                                                                                             |                                  | SPANSIO                                                                   | N. |

6

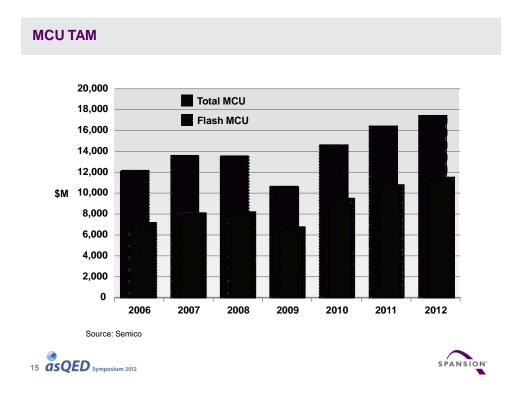

### **Embedded Flash in Microcontrollers (MCU)**

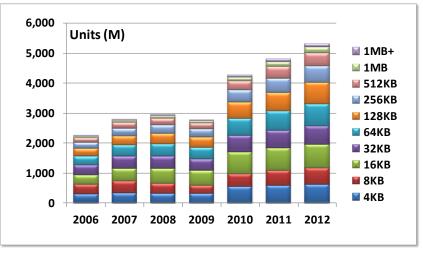

### MCU Volume by Embedded Flash Density

### **Embedded NOR Flash**

| NOR Flash<br>- Standalone<br>- Embedded in SOC                                | 2 |

|-------------------------------------------------------------------------------|---|

| NAND Flash<br>– Status and Market<br>– NAND Scaling Cha<br>– Lithography Gaps |   |

| Other Nonvolatile<br>- Phase Change Me<br>- Resistive RAM<br>- MRAM           | - |

| Summary                                                                       |   |

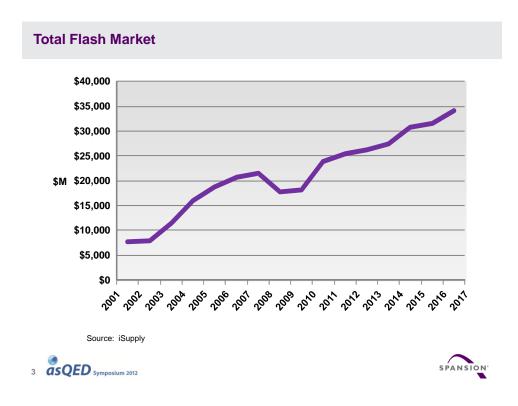

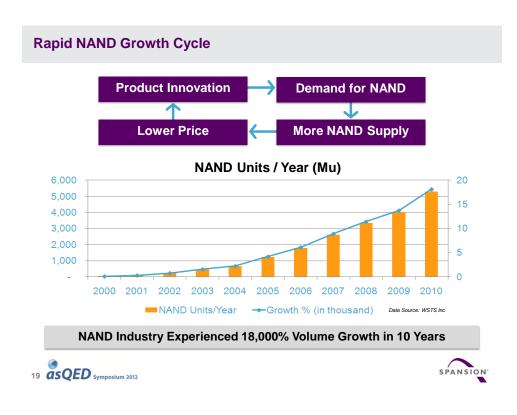

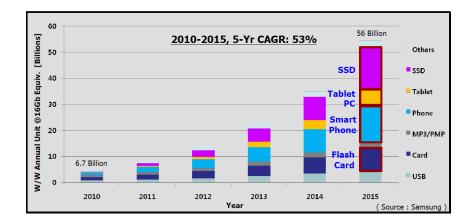

### NAND Flash Market Outlook

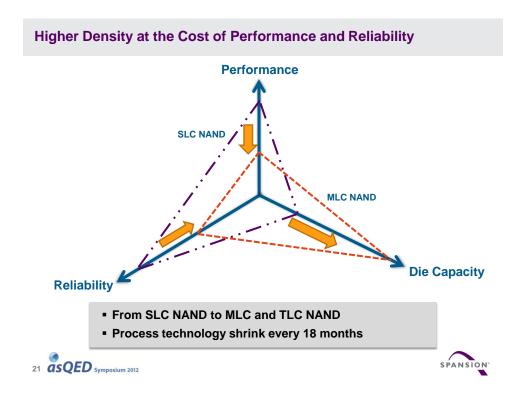

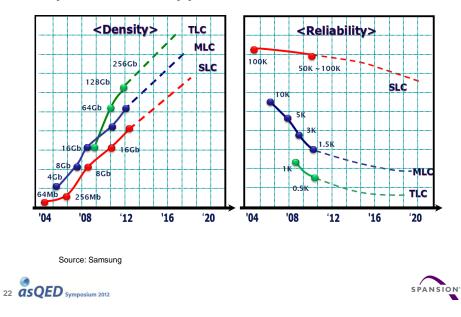

### **NAND Technology Migration**

Density has doubled every year since 2004

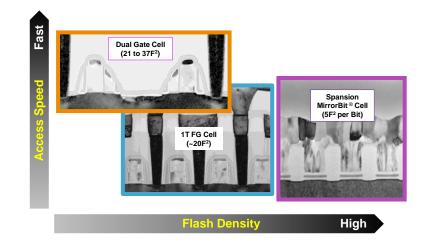

## NAND Cell and Architecture

### **Array Interconnections**

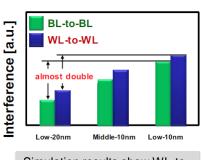

### Scaling Challenges in NAND: Interference

Simulation results show WL-to-WL and BL-to-BL interferences double going from low-20nm to low-10nm node

SPANSION

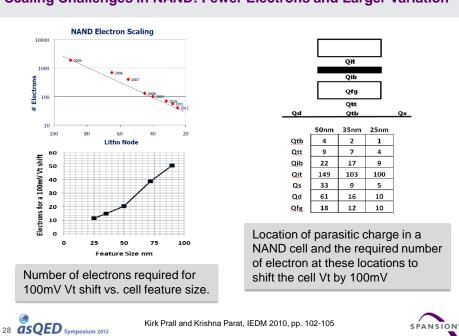

# Scaling Challenges in NAND: Fewer Electrons and Larger Variation

### Floating-Gate NAND Scaling Limitation

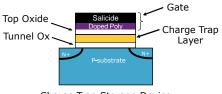

### Alternative NAND Architecture: Planar Charge Trap NAND

Cell Size 4.0F<sup>2</sup>

Charge Trap Storage Device

- Charge Trap cell in standard NAND array architecture

- Planar architecture

- Reduced interference coupling of neighboring cell

SPANSION

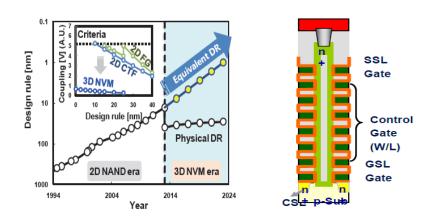

### **Alternative NAND Architecture: 3D**

Jungdal Choi and Kwang Soo Seol, VLSI Tech. Digest, 178-179, 2011

| NOR Flash<br>- Standalone<br>- Embedded in SOC                                    |      |

|-----------------------------------------------------------------------------------|------|

| NAND Flash - Status and Market Needs - NAND Scaling Challenges - Lithography Gaps |      |

| Other Nonvolatile Technolo<br>– Phase Change Memory<br>– Resistive RAM<br>– MRAM  | gies |

| <ul> <li>Phase Change Memory</li> <li>Resistive RAM</li> </ul>                    | gies |

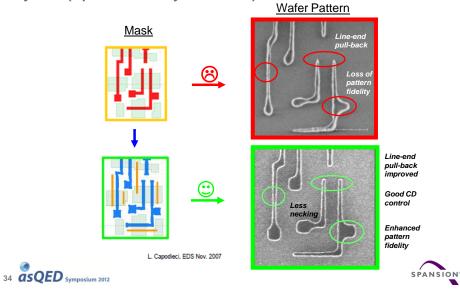

### Technique to Extend Litho Tool Capability (A)

### **RET (Resolution Enhancement Technology)** by OPC (Optical Proximity Correction)

### DFM (Design for Manufacturability): Changing cell layout to improve lithography performance Vertical pattern for active Irregular active and gate patterns Horizontal pattern for gate Difficult to print - requires intensive OPC Easy to print Gate Diffusion Gate Yan Borodovsky, Intel. 2006 SPIE Microlithography, San Jose, CA SPANSION 35 **asQED** Symposium 2012 Technique to Extend Litho Tool Capability (C) Double (or Quadruple) Patterning to extend process window by relaxing pitch to achieve fine patterns Example 1 (Litho-Litho-Etch) 1) Print the1st pattern 2) Coat and print the 2nd 3) Transfer the lithography with 2X pitch pattern between the pattern to the hardmask formed 1st pattern and substrate Example 2 (Self-Aligned Double 1) Print and form the 1st 2) Film deposition and 3) Transfer the spacer to Patterning) pattern with 2X pitch etch to form the the substrate layer spacer as hardmask Quadruple patterning can further achieve 2x more pattern density

36 **asQED** Symposium 2012

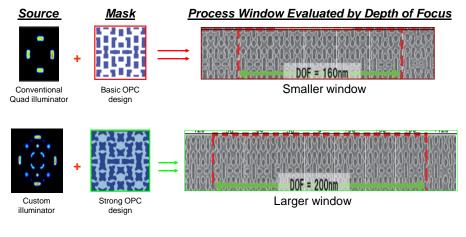

**Technique to Extend Litho Tool Capability (B)**

SPANSION

### Technique to Extend Litho Tool Capability (D)

SMO (Source-Mask Optimization) to extend process window by optimizing illuminator and OPC based on layout pattern

Naoya Hayashi, DNP, 2012 NIKON Litho Vision Presentation

37 **asQED** Symposium 2012

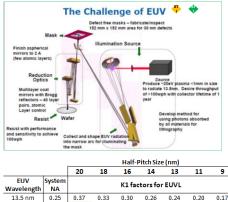

### Next Generation Lithography Tool: EUV

### 0.17 0.33 0.44 0.39 0.34 0.32 0.27 0.22 0.49 0.35 0.52 0.41 0.36 0.34 0.29 0.23 0.47 0.40 0.59 0.53 0.47 0.41 0.39 0.33 0.27 0.45 0.67 0.60 0.53 0.43 0.37 0.30 0.47 0.50 0.48 0.41 0.33 0.74 0.67 0.59 0.52 6.7nm 0.20 0.60 0.54 0.48 0.42 0.39 0.33 0.27 0.72 0.90 0.30 0.81 0.63 0.58 0.49 0.40 0.84 0.78 0.66 0.40 0.96 0.54 1.07

### **Technical Challenges**

- EUV source intensity Low wafer throughput

- Mask inspection Embedded defect in the blank

- Mirror reflectivity / contamination Cleaning frequency / downtime

- · Resist maturity Still in development

### 16nm half-pitch EUV resist lines

J.K. Stowers et. al., Proc. of SPIE Vol. 7969, 2011

SPANSION

More advanced EUV system under development to achieve < 10nm half-pitch

Katsuhiko Murakami, NIKON, From 2012 NIKON Litho Vision Presentation

asoeb Symposium 2012

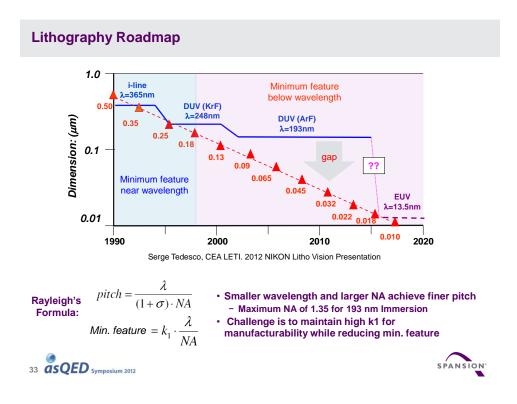

### Lithography Trend

- ArF (193nm) lithography already extended to 1X nm node

- More innovative approaches under development to further extend ArF capability

- EUV lithography significantly improved

- Need to resolve manufacturing challenges

- Target technology: 16nm node or smaller

# SPANSION

| NOR Flash<br>- Standalone<br>- Embedded in SOC                                          |          |

|-----------------------------------------------------------------------------------------|----------|

| NAND Flash<br>- Status and Market Need<br>- NAND Scaling Challeng<br>- Lithography Gaps |          |

| Other Nonvolatile Tech<br>– Phase Change Memory<br>– Resistive RAM<br>– MRAM            | nologies |

| - MRAM<br>Summary                                                                       |          |

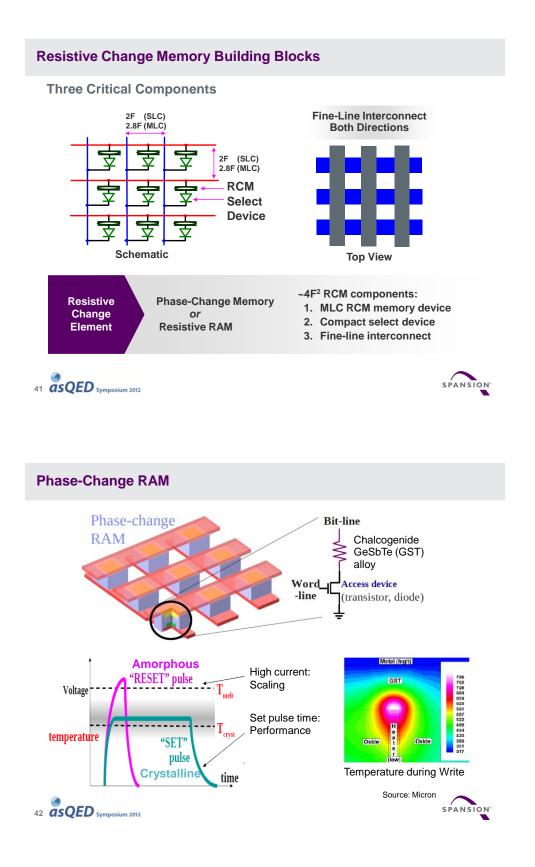

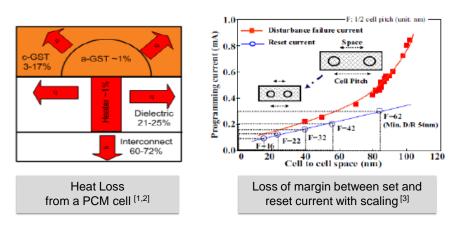

### Phase Change Memory Scaling Challenges

[1] S. Sadeghipour, ITHERM, 2006

[2] J. Tominga, et al., EPCOS, 2010

[3] S. Raox, et al, Phase Change Materials Science and Application, Spring 2009.

43 asQED Symposium 2012

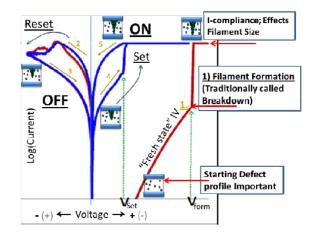

### **Conductive Bridge RAM (CBRAM)** forming cycle compliance level Metal\*-ions - cycle n - cycle n+1 Current [µA] Ag-rich precipitates 03 -0.2 0.1 0.2 03 Electrons ON-state OFF-state Voltage [V] Schematic illustration of the CBRAM conduction DC switching mechanism 1E+7 ON-resistance [Ohm] 1E+6 1E+5 1E+4 1E+3 1E+2 0.01 1000 0.1 10 100 1 Program current limit [µA] ON- state resistance dependence on programming current Micheal Kund, et al., IEDM, 2005 & NVMTS, 07 SPANSION 44 **asQED** Symposium 2012

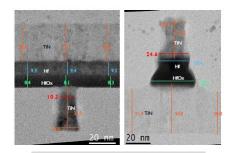

### **Oxygen Vacancy Based RRAM**

DC bi-polar switching characteristics. Oxygen vacancies convert the dielectric into a metal-rich filament (ON state) and reset (off state) by oxidation of the narrower tip of the conductive filament.

D. C, Gilmer, IMW, IEDM, 2012

### Oxygen Vacancy-based Resistive RAM

Memory Stack: TiN/10nm HfO2/10nm Hf/TiN

B. Govoreanu, et el, IEDM, 2011 46 **asQED** Symposium 2012

SPANSION

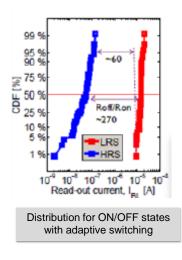

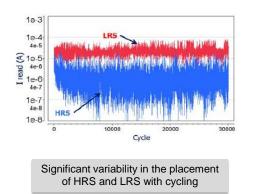

### **Issues with O-RRAM**

Kirk Prall, et al., Memory Workshop (IMW), pg. 1-5, 2012

47 asQED Symposium 2012

### In Production: Toggle MRAM

- Magnetic thin film as a storage element

- SRAM random access speed-35nm Read & Write Cycle time

- Magnetic Polarization rather than charge storage

- Densities of 256kb-16Mb in production (180nm-130nm)

- Challenging to scale to small geometries & reduce write current

- Nonvolatile memory market continues to grow with evolution of smarter and lighter portable products

- Flash memory is now leading the semiconductor industry in requiring the most advanced lithography technologies

- NOR and NAND Flash provide different value to the systems and will continue to coexist

- Active research in alternative Nonvolatile memories to address performance or scalability challenges of traditional Nonvolatile memory technologies